代寫博士論文選題:多通道高精度模數轉換器芯片探討與設計

本文是一篇博士論文,本文研究的核心在于優化多通道高精度模數轉換器芯片中的精度、ENOB和動態范圍等關鍵指標,實現這些指標在多通道架構選取、核心高精度ADC設計以及校正算法開發中的有機統一。

第一章 緒論

1.1 研究背景及意義

自上個世紀70年代中期起,基于硅襯底的互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor, CMOS)工藝的進步和數字信號處理器(Digital Signal Processor, DSP)能力的提升,對軍用設備、消費電子、儀器儀表、人工智能等領域帶來了革命性的發展[1-7]。這種進步顯著改變了信息獲取和處理方式,對我們的生活、工作和學習產生了深遠影響。在此過程中,模數轉換器(Analog-to-Digital Converter,ADC)和數模轉換器(Digital-to-Analog Converter,DAC)作為現實模擬世界與數字世界之間的橋梁,具有極其重要的作用。它們經常成為限制系統性能的重要因素。一般情況下,系統通過傳感器將現實世界的聲、光、力、熱、電等信息轉換為電信號。ADC和DAC在模擬域與數字域之間實現信號的轉換,統稱為數據轉換器。在數字域內,利用數字信號處理的強大計算能力,可以快速處理和整合大量信息,為用戶提供信息和決策依據。

模數轉換器(Analog-to-Digital Converter,ADC)具有多種不同的結構,根據是否需要過采樣,總體上可分為奈奎斯特轉換器與非奈奎斯特轉換器。奈奎斯特轉換器中,量化速度最快的類型為并行全閃(Flash)型模數轉換器。并行全閃型ADC采用一個電阻串并行產生多個參考電壓,并通過多個比較器在一個周期內得到輸出碼字[8-10]。由于該結構特點,當轉換器分辨率增加時,比較器個數呈指數增長,功耗和面積開銷巨大,可通過引入兩步式Flash ADC緩解硬件和功耗開銷[10-12]。流水線型ADC(Pipeline ADC)是一種廣泛應用于高速、高精度模數轉換架構[13-14],它將模數轉換過程分為多個階段,每個階段依次逼近最終的數字結果,從而實現高效的轉換。由于該類ADC每個階段需要增益放大器、比較器和DAC等組件,設計難度較高,對制造工藝要求也較高[15]。其次,流水線型ADC需要精確的校準,每個階段的增益和失真需要嚴格控制,否則誤差會在各個階段累積,影響轉換精度[16]。逐次逼近型模數轉換器(SAR ADC)是一種廣泛應用的ADC類型,其通過逐步逼近輸入模擬信號的數字值來完成轉換過程。

1.2 國內外研究現狀及發展趨勢

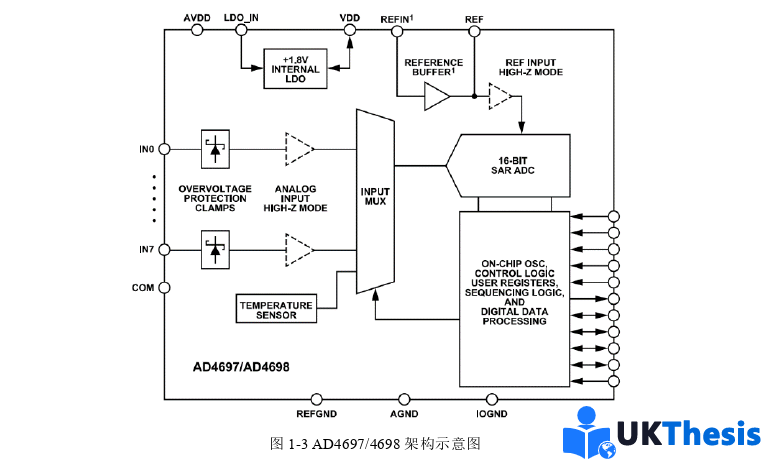

國外較早開始對高精度模數轉換器進行深入研究,其技術水平和設計流程已較為成熟。在高精度逐次逼近寄存器型模數轉換器的相關研究方面,許多公司和高等教育機構都取得了顯著進展。在這一領域,逐次逼近寄存器(SAR)ADC架構以及以SAR ADC為基礎的其他混合ADC架構已被廣泛應用并得到充分發展,涉及的公司包括亞德諾(Analog Devices, ADI)、德州儀器(Texas Instruments, TI)、美信(Maxim Integrated)等。

這些公司在SAR ADC技術研究與開發方面有著長期的積累和實踐經驗。其成熟的技術平臺和設計方法使它們在高精度逐次逼近寄存器型模數轉換器領域處于領先地位,尤其在ADC器件的高性能、低功耗以及面向不同應用場景的可定制化方面都取得了顯著的成就。此外,在SAR ADC技術研究與開發方面的成果不僅在商業應用中有所體現,同時也為學術界提供了許多技術參考和研究方向。其在工程實踐和學術探索方面的雙重貢獻,推動了高精度逐次逼近寄存器型模數轉換器技術的不斷進步和創新。

第二章 模數轉換器指標和類型概述

2.1 模數轉換器基本原理

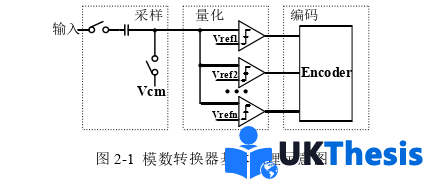

模數轉換器作為電子系統中不可或缺的關鍵組件,搭建起了模擬信號與數字信號之間的橋梁,將物理世界中的模擬信號,與數字世界中的二進制信號連接起來。ADC的功能在于將連續的模擬信號轉換為離散的數字信號,為后續的數字信號處理、存儲和傳輸提供基礎。模數轉換器將模擬信號轉換為數字信號的過程中,采樣保持、量化和編碼是三個核心步驟,如圖2-1所示。

采樣是模數轉換器獲取輸入信號幅度信息的第一步。模擬信號是一個隨時間連續變化的信號,而數字信號是離散的,因此必須將模擬信號離散采集。根據奈奎斯特采樣定理,為避免頻譜混疊導致的不可逆失真,模擬信號的采樣頻率應不低于信號最高頻率成分的兩倍,才能保證完整地重構原始信號。如果采樣頻率低于這個標準,將會產生混疊現象,導致信號失真。

2.2 模數轉換器性能指標

模數轉換器性能指標是標定ADC性能的重要依據,既可以幫助ADC設計者明確模數轉換器各個子模塊的設計重點,也方便ADC使用者依據應用場景進行橫向比對選型。

總的來說,模數轉換器的性能指標主要分為靜態指標和動態指標。其中,靜態指標包括量化誤差(Quantization Error)、失調(Offset)、增益誤差(Gain Error,GE)、微分非線性(DNL)、積分非線性(INL)、溫度系數(Temperature Coefficient, TC)等。而ADC 的動態指標包含信噪比(Signal to Noise Ratio, SNR)、無雜散動態范圍(Spurious Free Dynamic Range, SFDR)、信號噪聲失真比(Signal to Noise and Distortion, SNDR)、有效位(Effective Number of Bits, ENOB)、總諧波失真(Total Harmonic Distortion, THD)和優值(Figure of Merit,FoM)。下面本文將對這些指標進行簡要介紹。

第三章 多通道高精度 SAR ADC 架構和關鍵技術 ........................... 28

3.1 常規多通道ADC結構 ............................ 28

3.2 本文多通道ADC結構 ........................... 29

3.3 高精度 SAR ADC 關鍵技術 .................... 30

第四章 多通道高精度模數轉換器關鍵模擬電路設計 ........................ 44

4.1 模擬前端驅動電路 ............................... 44

4.2 采樣保持(S/H)電路 ......................... 51

第五章 多通道高精度模數轉換器校正技術 ................... 72

5.1 模數轉換器校正技術 .............................. 72

5.1.1 模擬前端增益和偏移自校正 ..................... 72

5.1.2 數字后臺校正 ....................... 73

第六章 多通道高精度模數轉換器的物理實現及測試分析

6.1 測試環境搭建

SAR ADC的測試主要包括功能測試和性能測試。其包含的測試內容和測試方法如下:

1.功能測試:

1) 輸入范圍測試:驗證ADC是否能夠處理預期范圍內的模擬輸入信號。通過輸入不同幅度和頻率的信號,觀察ADC輸出是否在預期范圍內。 2) 分辨率測試:驗證ADC的分辨率是否符合規格。通過輸入階梯波信號,觀察ADC的輸出是否能夠準確分辨每個階梯。 3) 線性度測試:驗證ADC的輸入輸出關系是否線性。通過輸入已知斜率和截距的線性信號,比較ADC的實際輸出與理論輸出之間的差異

2. 性能測試:

1) 靜態誤差測試:包括偏移誤差、增益誤差和微分非線性誤差等。這些誤差可以通過輸入特定的測試信號并測量ADC的輸出來計算。 2) 動態性能測試:主要關注ADC的頻譜性能,如信噪比(SNR)、無雜散動態范圍(SFDR)和總諧波失真(THD)等。這些參數可以通過輸入正弦波信號并測量ADC的輸出來評估。

第七章 總結與展望

7.1 全文總結

本文針對多通道高精度SAR ADC在現代電子系統中的重要性及其當前設計挑戰進行了深入研究。研究的核心在于優化多通道高精度模數轉換器芯片中的精度、ENOB和動態范圍等關鍵指標,實現這些指標在多通道架構選取、核心高精度ADC設計以及校正算法開發中的有機統一。

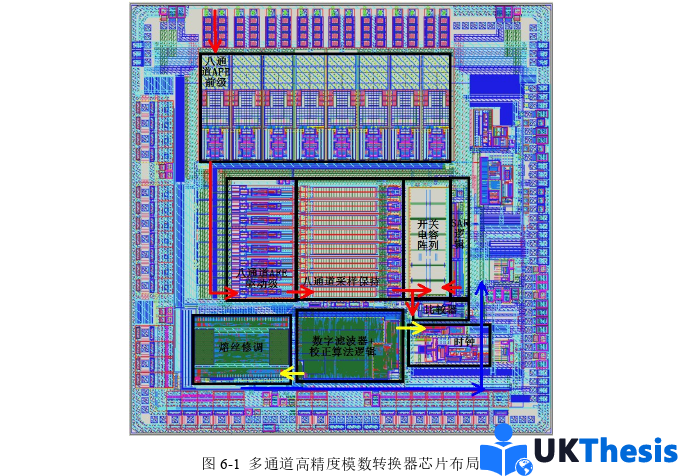

在多通道高精度模數轉換器的電路架構方面,對現有實現方式進行了深入分析,評估了不同電路結構在性能、面積和校正開銷方面的優缺點。基于這些分析,設計了一種適用于多通道和高精度需求的模數轉換器電路架構。

在高精度模擬前端設計方面,不僅實現了抗混疊和驅動功能,還設計了具有高線性度的8通道模擬前端。同時,對于高精度模數轉換器的核心設計,詳細探討了高精度DAC電容陣列、高精度比較器和低溫漂基準等關鍵電路模塊的設計要求與難點,并成功設計出一款采樣率為200kSPS的18位逐次逼近模數轉換器芯片。

針對多通道高精度模數轉換器中的非理想因素,深入分析了其來源和作用機理,并提出了針對模擬前端通道間失配誤差、電容失配誤差和比較器失調等問題的校正算法。測試結果顯示,在200kSPS(無過采樣)模式下,設計的ADC芯片ENOB為14.21bits,SNR為88.7dB,SNDR為87.3dB,SFDR為93.15dB,THD為-93dB,功耗69.53mW,通道串擾低于-120dB。

參考文獻(略)